はじめに

FO-WLP (Fan-Out Wafer Level Package)とFO-PLP (Fan-Out Panel Level Package)について勉強したことを逐一まとめていきます。

以下のXのスレッドに追記しつつ、この記事に加筆していきます。

用語の分解・意味

FO-WLP (Fan-Out Wafer Level Package), FO-PLP (Fan-Out Panel Level Package)を構成する、「パッケージ(半導体パッケージ)」「Fan-Out Package」「WLP (Fan-Out Wafer Level Package)」「PLP (Fan-Out Panel Level Package)」の意味を明確にする。

半導体パッケージ

半導体パッケージが果たす役割は、①ICチップを外部環境(衝撃や汚染など)から保護、②外部のプリント基板との電気接続、③チップの放熱、④プリント基板への実装性向上、⑤複数チップをワンパッケージ化、などが主に挙げられる。

【参考】

半導体パッケージ基板とは | TOPPAN株式会社エレクトロニクス|リンク

半導体(IC)パッケージとは | 半導体(IC)パッケージ | 京セラ (kyocera.co.jp)|リンク

半導体パッケージの役割 | 事業内容 | 企業情報 | 新光電気工業 (shinko.co.jp)|リンク

Fan-Out Package (ファンアウト・パッケージ)

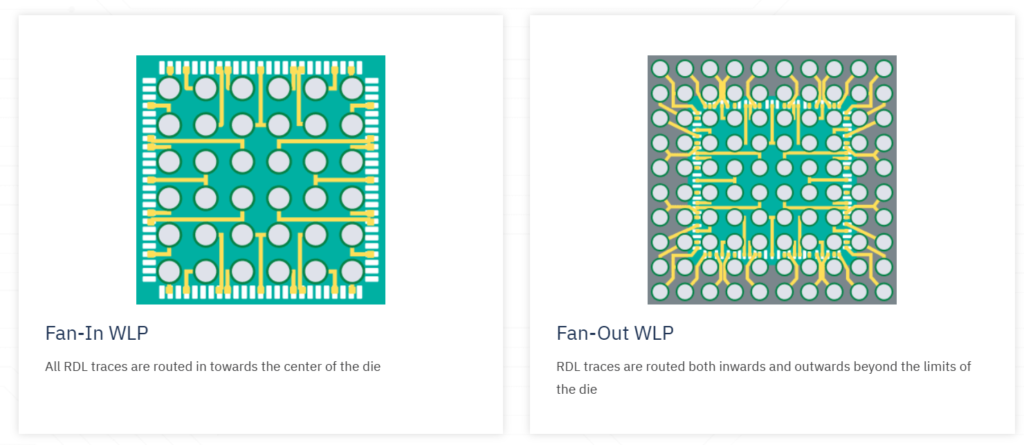

半導体パッケージング技術における「ファンアウト」とは、パッケージの入出力端子 (I/O)がシリコンダイよりも大きな面積に展開され、シリコンダイとパッケージをつなぐ配線群がシリコンダイの外側に引き回された状態。

逆に「ファンイン」とは、シリコンダイとパッケージをつなぐ配線群がシリコンダイの内側に引き回された状態。シリコンダイの入出力パッドは周辺あるいはエリアに配置されているのに対し、パッケージの入出力端子はエリアアレイ配置になっている。

【参考】

モバイル端末向けの最先端パッケージング技術:福田昭のデバイス通信(110) TSMCが解説する最先端パッケージング技術(9) – EE Times Japan (itmedia.co.jp)|リンク

Fan-Out Packaging | ASE (aseglobal.com)|リンク

リンク集

注目される新パッケージ技術「FOWLP」 – 東芝が語った今後の方向性 | TECH+(テックプラス) (mynavi.jp)|リンク

JEITA半導体部会, “小型・低コスト・高速化を支える半導体パッケージ技術”, 2015年3月6日|リンク

JEITA半導体部会, “小型・低コストパッケージとして実用化が始まるFO-WLP”, 2016年3月4日|リンク

野中敏央, “システムインテグレーション実装技術を牽引しはじめ 第 2 ステージに入ったファン・アウト・パッケージと これを支える材料”, エレクトロニクス実装学会誌 Vol. 20 No. 1 (2017)|リンク

SEMI, “FO-PLP製造工程及び主な技術課題についての紹介”, 2018年7月25日|リンク

モバイル端末向けの最先端パッケージング技術:福田昭のデバイス通信(110) TSMCが解説する最先端パッケージング技術(9) – EE Times Japan (itmedia.co.jp)|リンク

モバイル端末向けパッケージング技術「FOWLP」(前編):福田昭のデバイス通信(111) TSMCが解説する最先端パッケージング技術(10) – EE Times Japan (itmedia.co.jp)|リンク

モバイル端末向けパッケージング技術「FOWLP」(後編):福田昭のデバイス通信(112) TSMCが解説する最先端パッケージング技術(11)(1/2 ページ) – EE Times Japan (itmedia.co.jp)|リンク

コメント